왜 NVM Express인가?

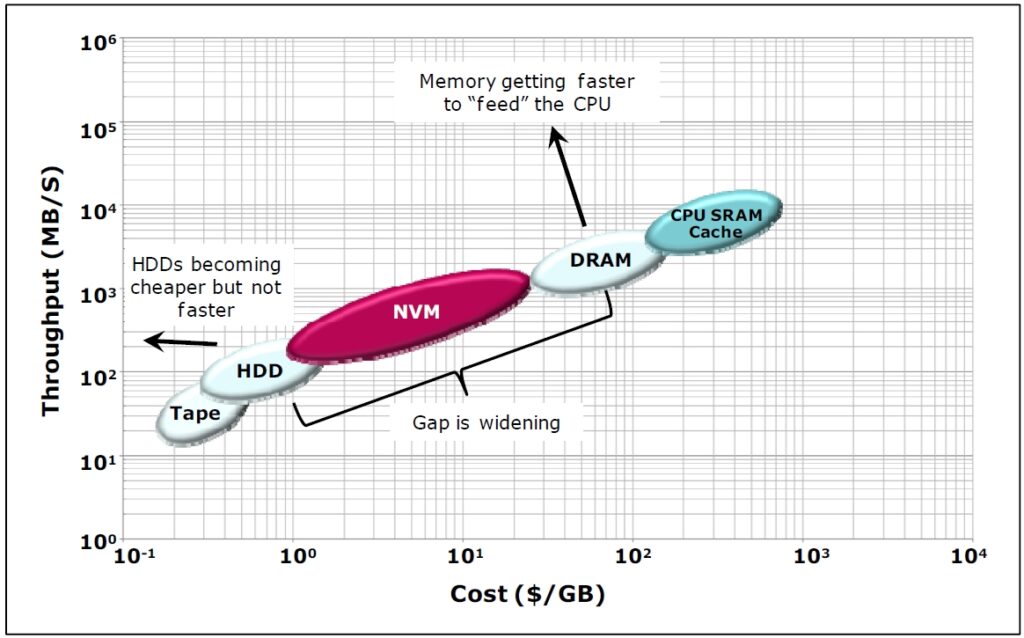

그림 1에서 볼 수 있듯이 DRAM과 하드 드라이브의 가격 대비 성능 격차가 점점 더 커지고 있습니다.

시스템에서 솔리드 스테이트 드라이브(SSD) 형태의 NVM이 이 격차를 메우며 시스템에 ‘I/O 메모리 계층’을 생성하고 있습니다.

그림 1: 가격/성능 격차를 메우는 NVM

플랫폼의 PCI Express(PCIe) 연결성은 계속 증가하고 있습니다. 예를 들어, 인텔® 5000 칩셋에는 24개의 PCIe Gen1 레인이 포함되어 있으며, 인텔® 5520 칩셋에서는 36개의 PCIe Gen2 레인으로 확장되어 레인 수가 증가하고 레인당 대역폭이 두 배로 증가했습니다. PCIe는 오늘날 최고 성능의 I/O 인터페이스로, PCIe Gen3에서는 레인당 1GB/s를 제공합니다.

오늘날 PCIe SSD는 타의 추종을 불허하는 성능으로 시장에 출시되고 있습니다. 많은 PCIe SSD가 8레인의 PCIe Gen2를 지원하여 3GB/s 이상을 제공합니다. PCIe Gen3로 전환하면 단일 장치에서 제공할 수 있는 대역폭이 6GB/s로 두 배가 됩니다. 더 빠른 인터페이스와 칩셋 또는 CPU에 직접 연결할 수 있는 기능 덕분에 지연 시간이 수 마이크로초까지 단축됩니다. 또한 칩셋이나 CPU에 직접 연결하면 외부 호스트 버스 어댑터가 필요하지 않아 7~10와트의 전력과 10달러 이상의 비용을 절약할 수 있습니다.

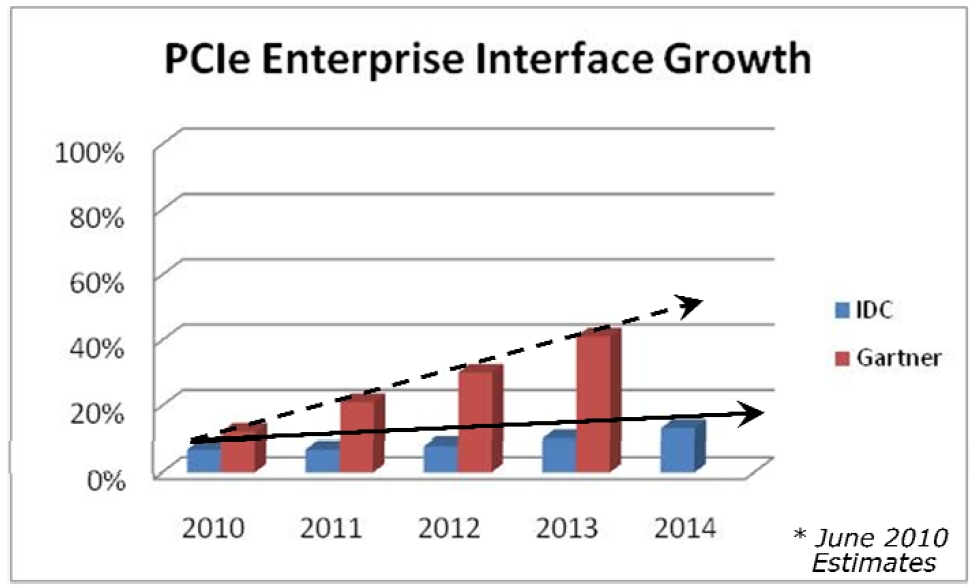

분석가들은 그림 2의 예측에서 볼 수 있듯이 엔터프라이즈 시장 부문에서 PCIe SSD에 큰 기회가 있을 것으로 보고 있습니다. 빠른 성장 곡선을 실현하려면 표준 드라이버와 일관된 기능 세트가 필요합니다.

그림 2: 엔터프라이즈 SSD의 PCIe 인터페이스 성장에 대한 애널리스트 전망

서로 다른 구현과 고유한 드라이버로 인해 PCIe SSD의 채택이 저해되고 있습니다. 각 SSD 공급업체는 OEM이 검증해야 하는 각 OS용 드라이버를 제공합니다. 각 SSD 공급업체는 서로 다른 방식으로 서로 다른 기능의 하위 집합을 구현하기 때문에 OEM은 불필요한 추가 검증 작업을 수행해야 합니다.

PCIe SSD의 빠른 채택과 상호 운용성을 위해 업계 리더들은 NVM Express 표준을 정의했습니다. 이 표준에는 레지스터 프로그래밍 인터페이스, 명령어 세트, 기능 세트 정의가 포함되어 있습니다. 이를 통해 각 OS에 맞는 표준 드라이버를 작성할 수 있고 구현 간의 상호 운용성을 구현하여 OEM 인증 주기를 단축할 수 있습니다.

NVM Express는 향후 확장 가능한 최적화된 명령어 세트를 정의하여 레거시 지원 요구 사항으로 인한 디바이스의 부담을 방지합니다. 그러나 SCSI 아키텍처 모델을 기반으로 구축된 기존 애플리케이션과 소프트웨어 인프라가 있습니다. 작업 그룹은 다음과 같이 원활하게 전환할 수 있도록 SCSI와 NVM Express 사양 간의 매핑을 정의하는 번역 문서를 정의하고 있습니다.

기존 소프트웨어 인프라에 대한 투자를 유지하면서 NVM Express로 원활하게 전환할 수 있습니다. 이 번역은 NVM Express 드라이버 내의 레이어로 수행될 수 있습니다. 이 문서는 5월에 공개될 예정입니다.

NVM Express 개요

NVM Express는 PCI Express 기반 솔리드 스테이트 드라이브를 사용하는 기업 및 클라이언트 시스템의 요구 사항을 해결하기 위해 설계된 확장 가능한 호스트 컨트롤러 인터페이스입니다. 이 인터페이스는 최적화된 명령 실행 및 완료 경로를 제공합니다. 이 인터페이스는 I/O 대기열 내에서 최대 64K 명령 대기열을 지원하여 병렬 작업을 지원합니다. 또한 엔드투엔드 데이터 보호(T10 DIF 및 DIX 표준과 호환), 향상된 오류 보고 및 가상화와 같은 다양한 엔터프라이즈 기능에 대한 지원이 추가되었습니다.

인터페이스의 주요 특성은 다음과 같습니다:

- 명령 실행 또는 완료 경로에서 캐시할 수 없는 / MMIO 레지스터 읽기가 필요하지 않습니다.

- 명령 실행 경로에서 최대 한 번의 MMIO 레지스터 쓰기가 필요합니다.

- 최대 64K 개의 I/O 대기열을 지원하며, 각 I/O 대기열은 최대 64K 개의 명령을 지원합니다.

- 잘 정의된 중재 메커니즘으로 각 I/O 대기열에 연결된 우선 순위.

- 4KB 읽기 요청을 완료하기 위한 모든 정보가 64B 명령 자체에 포함되어 효율적인 소규모 랜덤 I/O 작업을 보장합니다.

- 효율적이고 간소화된 명령어 세트.

- MSI/MSI-X 및 인터럽트 집계를 지원합니다.

- 여러 네임스페이스를 지원합니다.

- SR-IOV와 같은 I/O 가상화 아키텍처를 효율적으로 지원합니다.

- 강력한 오류 보고 및 관리 기능.

이 사양은 다음 기능을 포함하는 간소화된 레지스터 세트를 정의합니다.

- 컨트롤러 능력 표시

- 장치 고장 상태(명령 상태는 CQ를 통해 직접 처리)

- Admin Queue 구성(Admin 명령을 통해 처리되는 I/O Queue 구성)

- 제출 및 완료 대기열의 확장 가능한 개수를 위한 초인종 레지스터

컨트롤러가 지원하는 기능은 Controller Capabilities(CAP) 레지스터에 표시되며 식별 명령에 반환된 Controller 및 Namespace 데이터 구조의 일부로 표시됩니다. Identify Controller 데이터 구조는 전체 컨트롤러에 적용되는 기능과 설정을 나타냅니다. Identify Namespace 데이터 구조는 특정 네임스페이스에 특정한 기능과 설정을 나타냅니다.

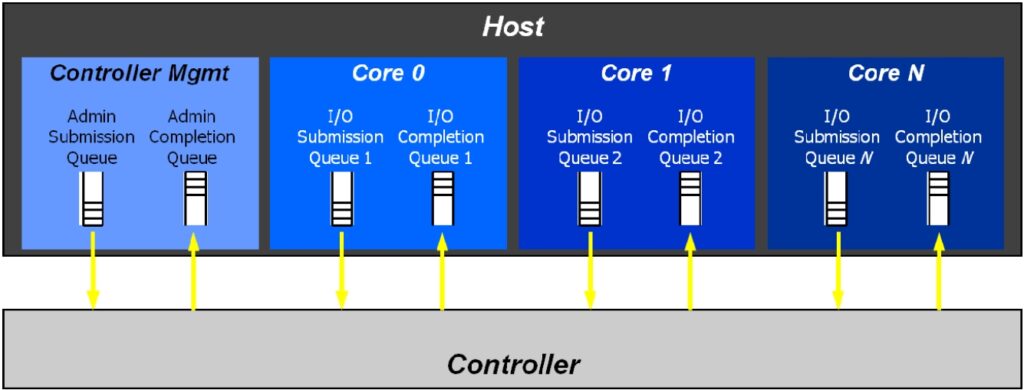

향상된 NVMHCI는 쌍을 이루는 Submission 및 Completion Queue 메커니즘을 기반으로 합니다. 명령은 호스트 소프트웨어에 의해 Submission Queue에 배치됩니다. 완료는 컨트롤러에 의해 연결된 Completion Queue 에 배치됩니다. Multiple Submission Queue이 동일한 Completion Queue을 활용할 수 있습니다. Submission 및 Completion Queue은 호스트 메모리에 할당됩니다.

Admin Submission 및 관련 Completion Queue 은 장치 관리 및 제어(예: I/O 제출 및 완료 대기열 생성 및 삭제, 명령 중단 등)를 위해 존재합니다. 관리 명령 세트의 일부인 명령만 실행될 수 있습니다. 관리자 제출 대기열.

I/O Command Set 세트는 I/O 대기열 쌍과 함께 사용됩니다. 이 사양은 NVM Command Set라는 하나의 I/O Command Set를 정의합니다.

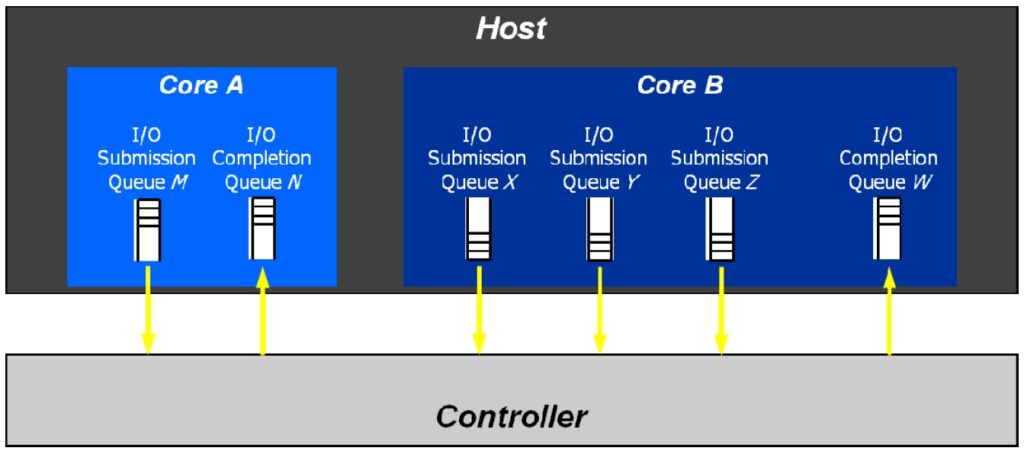

호스트 소프트웨어는 컨트롤러가 지원하는 최대 한도까지 대기열을 생성합니다. 일반적으로 생성되는 명령 대기열 수는 시스템 구성 및 예상 작업 부하에 따라 결정됩니다. 예를 들어, 4개 코어 프로세서 기반 시스템에서는 잠금을 방지하고 적절한 프로세서 코어의 캐시에 데이터 구조가 생성되도록 하기 위해 코어당 대기열 쌍이 있을 수 있습니다. 그림 3은 Submission Queue과 Completion Queue 간의 1:1 매핑을 보여주는 대기열 쌍 메커니즘의 그래픽 표현을 제공합니다. 그림 4는 여러 I/O 제출 대기열이 코어 B에서 동일한 I/O 완료 대기열을 활용하는 예를 보여줍니다.

그림 3: 대기열 쌍 예, 1:1 매핑

그림 4: 대기열 쌍 예, n:1 매핑

SQ(Submission Queue)는 컨트롤러가 실행할 명령을 제출하기 위해 호스트가 사용하는 고정된 슬롯 크기를 가진 순환 버퍼입니다. 호스트는 적절한 SQ Tail 초인종 레지스터를 업데이트합니다.

실행할 새 명령은 1~n개입니다. 새로운 초인종 레지스터 쓰기가 있으면 컨트롤러에서 이전 SQ Tail 값을 덮어씁니다. 컨트롤러는 Submission Queue에서 순서대로 SQ 항목을 가져오지만 해당 명령을 어떤 순서로든 실행할 수 있습니다.

각 Submission Queue 항목은 명령입니다. 명령의 크기는 64바이트입니다. 데이터 전송에 사용할 호스트 메모리의 물리적 메모리 위치는 Physcial Region Page(PRP) 항목을 사용하여 지정됩니다. 각 명령에는 두 개의 PRP 항목이 포함될 수 있습니다. 데이터 버퍼를 설명하기 위해 두 개 이상의 PRP 항목이 필요한 경우 PRP 항목 목록을 설명하는 PRP 목록에 대한 포인터가 제공됩니다.

CQ(Completion Queue)는 완료된 명령의 상태를 게시하는 데 사용되는 고정 슬롯 크기를 가진 순환 버퍼입니다. 완료된 명령은 연관된 SQ 식별자의 조합으로 고유하게 식별됩니다.

호스트 소프트웨어에 의해 할당된 명령 식별자입니다. 여러 Submission Queue이 단일 Completion Queue과 연결될 수 있습니다. 이 기능은 해당 명령이 여러 Submission Queue에서 시작된 경우에도 단일 작업자 스레드가 하나의 Completion Queue을 통해 모든 명령 완료를 처리하는 경우에 사용할 수 있습니다. CQ 헤드 포인터는 마지막 무료 CQ 항목을 나타내는 완료 항목을 처리한 후 호스트 소프트웨어에 의해 업데이트됩니다. Phase(P) 비트는 완료 항목에 정의되어 레지스터에 문의하지 않고 항목이 새로 게시되었는지 여부를 나타냅니다. 이를 통해 호스트 소프트웨어는 새 항목이 이전 또는 현재 완료 알림 라운드의 일부로 게시되었는지 여부를 확인할 수 있습니다. 특히, Completion Queue 위치를 통과하는 각 라운드마다 컨트롤러는 단계 비트를 반전시킵니다.

기업 및 고객 권장 사항

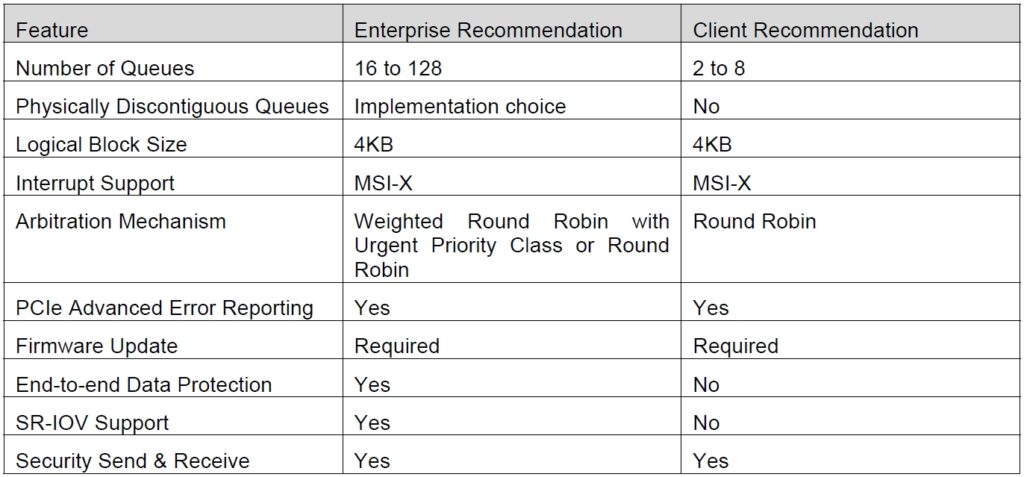

NVM Express는 유연한 사양으로 클라이언트 및 엔터프라이즈 시장 부문의 요구 사항을 포괄하는 솔루션을 구축할 수 있습니다. 그림 5는 엔터프라이즈 또는 클라이언트 시스템용으로 구축된 SSD에 권장되는 기능을 정의합니다.

그림 5: 기업 및 고객 권장사항

출처 : https://nvmexpress.org/resource/nvm-express-explained/